Description

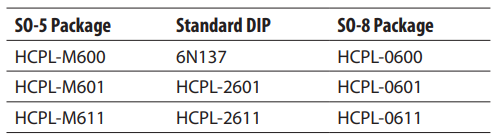

These small outline high CMR, high speed, logic gate opto coup lers are single channel devices in a five lead miniature foot print. They are electrically equivalent to the following Avago optocouplers (except there is no output enable feature):

The SO-5 JEDEC registered (MO-155) package outline does not require “through holes” in a PCB. This package occupies approximately one fourth the footprint area of the standard dual-in-line package. The lead profile is designed to be com patible with standard surface mount processes.

The HCPL-M600/01/11 optically coupled gates combine a GaAsP light emitting diode and an integrated high gain photon detector. The output of the detector I.C. is an Open-collector Schottky-clamped transistor. The internal shield provides a guaranteed common mode

transient immunity specification of 5,000 V/μs for the HCPL-M601, and 10,000 V/μs for the HCPL-M611. This unique design provides maximum ac and dc circuit isolation while achieving TTL compatibility. The optocoupler ac and dc operational param eters are guaranteed from –40°C to 85°C allowing trouble free system performance.

Features

●? ?Surface Mountable

●? ?Very Small, Low Profile JEDEC Registered Package Outline

●? ?Compatible with Infrared Vapor Phase Reflow and Wave Soldering Processes

●? ?Internal Shield for High Common Mode Rejection (CMR)

HCPL-M601: 10,000 V/μs at VCM?= 50 V

HCPL-M611: 15,000 V/μs at VCM?= 1000 V

●? ?High Speed: 10 Mbd

●? ?LSTTL/TTL Compatible

●? ?Low Input Current Capability: 5 mA

●? ?Guaranteed ac and dc Performance over Temperature:–40°C to 85°C

●? ?Safety and regulatory approvals:

- UL recognized: 3750 Vac for 1 min. per U.L.(File No. 55361)

- CSA component acceptance Notice #5

- IEC/EN/DIN EN 60747-5-2 approved for HCPL-M601/M611 Option 060.

●? ?Lead Free Option

Applications

●? ?Isolated Line Receiver

●? ?Simplex/Multiplex Data Transmission

●? ?Computer-Peripheral Interface

●? ?Microprocessor System Interface

●? ?Digital Isolation for A/D, D/A Conversion

●? ?Switching Power Supply

●? ?Instrument Input/Output Isolation

●? ?Ground Loop Elimination

●? ?Pulse Transformer Replacement

?

?

?

?

?

?

Important Notice

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by F-tone Networks before they become applicable to any particular order or contract. In accordance with the F-tone Networks policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of F-tone Networks or others. Further details are available from any F-tone Networks sales representative.